Ahead-looking: TSMC is continuous preparations for its 2nm-class manufacturing course of applied sciences. The {hardware} is progressing properly, whereas third-party corporations and chip designers might want to adapt to the slew of improvements that N2 is bringing to the desk.

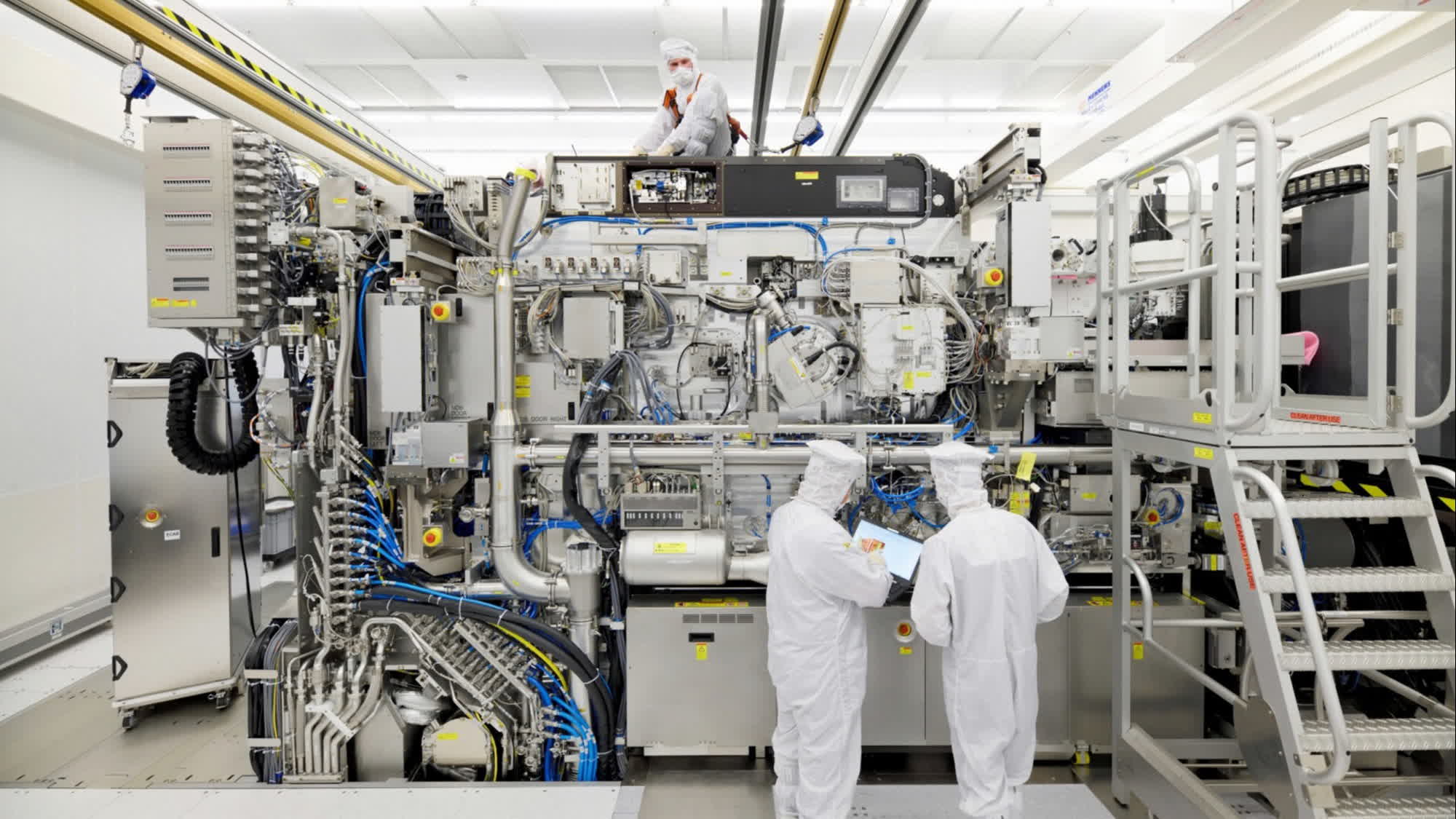

Within the subsequent few years, Taiwanese foundry TSMC will introduce a few of the most superior chip manufacturing applied sciences on the planet. The 2 nanometer-based N2, N2P, and N2X course of tech will embody a number of improvements, and all the ecosystem orbiting across the firm’s silicon enterprise is destined to vary accordingly.

As famous by AnandTech, N2 and its future iterations ought to deliver numerous enhancements to microchips, together with a discount in energy consumption (-25-30%), extra efficiency (+10-15%) and transistor density (>1.15x) in a “blended” chip configuration (50% logic, 30% SRAM, 20% analog). Mass manufacturing of 2nm chips ought to arrive within the second half of 2025, however TSMC is working with its prospects and companions 2 years upfront as a result of the “nanosheet is completely different.”

The N2 course of will embody improvements similar to nanosheet gate-all-around (GAA) transistors, bottom energy supply, and super-high-performance metal-insulator-metal (SHPMIM) capacitors. TSMC mentioned throughout its newest Open Innovation Platform discussion board in Europe that to benefit from such novel applied sciences, main chip designers want to make use of new digital design automation (EDA) simulation, verification, and IP instruments.

GAA transistors behave in a different way than FinFET ones, TSMC warned. Due to this fact, chip corporations must begin their design workloads basically from scratch. Creating new IPs primarily based on the 2nm course of improve will not be “more durable,” TSMC mentioned, simply completely different. Corporations must adapt to the brand new tech, identical to they went from planar transistors to a “3D” (FinFET) design prior to now.

Main producers of EDA software program (Cadence, Synopsys) have already been licensed by TSMC to work on N2, and chip builders can begin utilizing the brand new instruments instantly. Essentially the most advanced a part of the 2nm transition includes pre-built IP chip designs, as a result of TSMC continues to be constructing some blocks to be included within the aforesaid designs.

Customary components similar to GPIO/ESD, PLL, SRAM, and ROM are prepared each for cell and high-performance computing (HPC) purposes. Some parts exist in type of pre-silicon improvement kits, whereas others have already been examined in precise {hardware}. Different N2 blocks similar to non-volatile reminiscence, interface IP, and chiplet IP usually are not out there but, which might bottleneck chip design efforts. Third-party corporations similar to Alphawave, Cadence, Credo, and eMemory are already engaged on them, TSMC mentioned.